## UC1875/6/7/8 UC2875/6/7/8 UC3875/6/7/8

# Phase Shift Resonant Controller

## FEATURES

- Zero to 100% Duty Cycle Control

- Programmable Output Turn-On Delay

- Compatible with Voltage or Current Mode Topologies

- Practical Operation at Switching Frequencies to 1MHz

- Four 2A Totem Pole Outputs

- 10MHz Error Amplifier

- Undervoltage Lockout

- Low Startup Current –150µA

- Outputs Active Low During UVLO

- Soft-Start Control

- Latched Over-Current Comparator With Full Cycle Restart

- Trimmed Reference

## DESCRIPTION

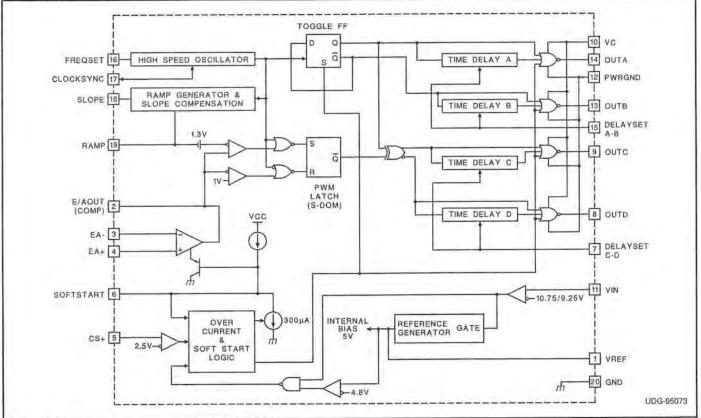

The UC1875 family of integrated circuits implements control of a bridge power stage by phase-shifting the switching of one half-bridge with respect to the other, allowing constant frequency pulse-width modulation in combination with resonant, zero-voltage switching for high efficiency performance at high frequencies. This family of circuits may be configured to provide control in either voltage or current mode operation, with a separate over-current shutdown for fast fault protection.

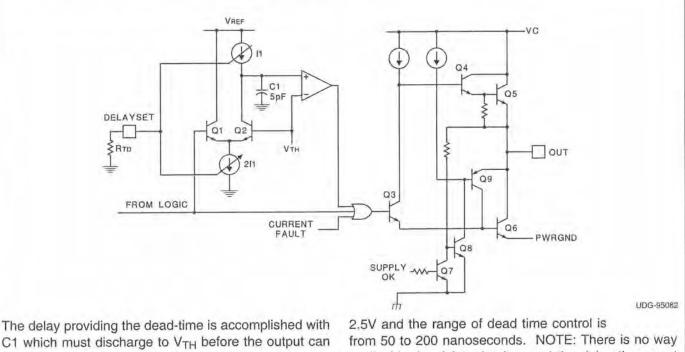

A programmable time delay is provided to insert a dead-time at the turn-on of each output stage. This delay, providing time to allow the resonant switching action, is independently controllable for each output pair (A-B, C-D).

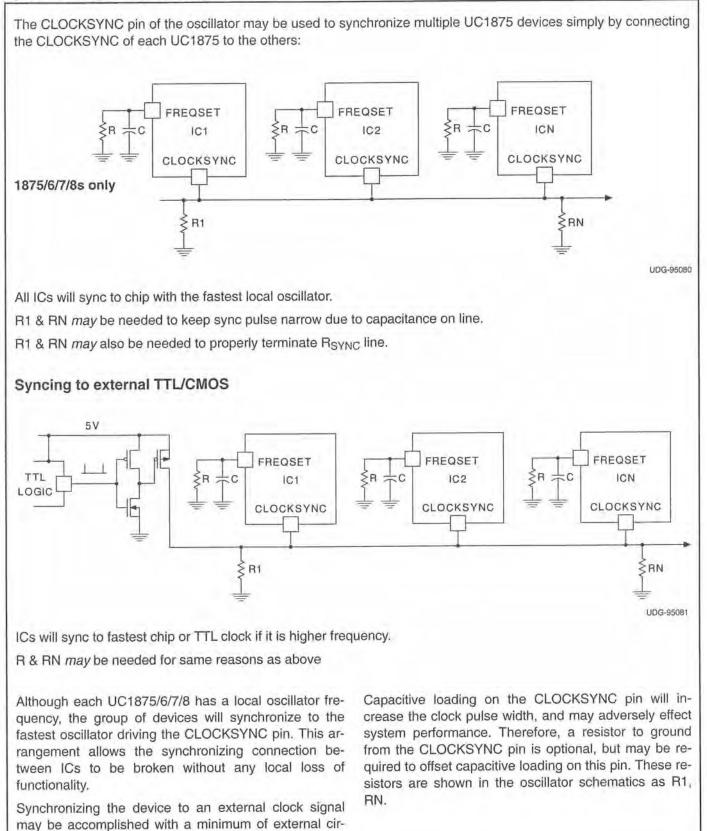

With the oscillator capable of operation at frequencies in excess of 2MHz, overall switching frequencies to 1MHz are practical. In addition to the standard free running mode, with the CLOCKSYNC pin, the user may configure these devices to accept an external clock synchronization signal, or may lock together up to 5 units with the operational frequency determined by the fastest device.

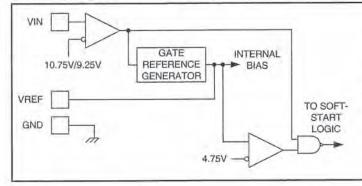

Protective features include an undervoltage lockout which maintains all outputs in an active-low state until the supply reaches a 10.75V threshold. 1.5V hysteresis is built in for reliable, boot-strapped chip supply. Over-current protection is provided, and will latch the outputs in the OFF state within 70nsec of a fault. The current-fault circuitry implements full-cycle restart operation. (continued)

## **BLOCK DIAGRAM**

SLUS229C - JULY 1999 - REVISED MAY 2007

#### DESCRIPTION (cont.)

Additional features include an error amplifier with bandwidth in excess of 7MHz, a 5V reference, provisions for soft-starting, and flexible ramp generation and slope compensation circuitry.

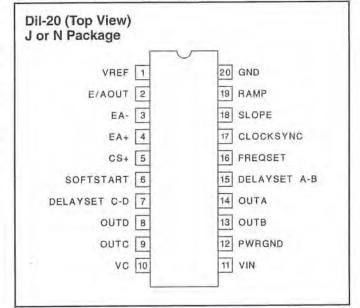

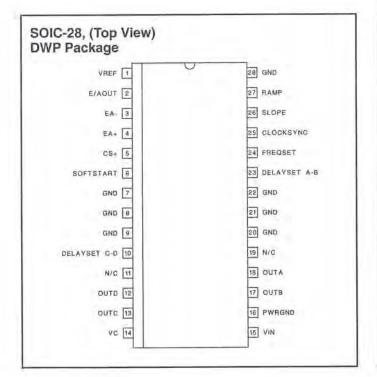

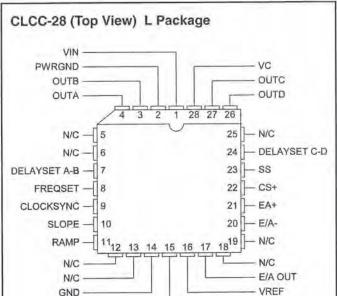

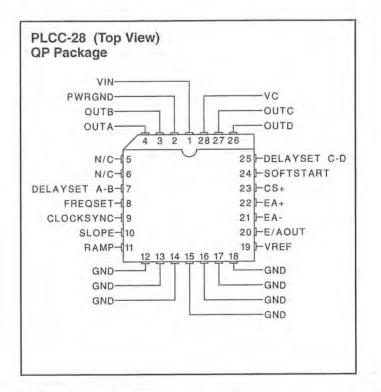

These devices are available in 20-pin DIP, 28-pin "bat-wing" SOIC and 28 lead power PLCC plastic packages for operation over both 0°C to 70°C and -25°C to +85°C temperature ranges; and in hermetically sealed cerdip, surface mount, and ceramic leadless chip carrier packages for -55°C to +125°C operation.

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage (VC, VIN)                                                                                                                                                                                                                                                | OV         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| DC                                                                                                                                                                                                                                                                      | 5A         |

| Pulse (0.5µs)                                                                                                                                                                                                                                                           | ЗA         |

| Analog I/Os                                                                                                                                                                                                                                                             |            |

| (Pins 1, 2, 3, 4, 5, 6, 7, 15, 16, 17, 18, 19)0.3 to 5.                                                                                                                                                                                                                 | ЗV         |

| Storage Temperature Range65°C to +150                                                                                                                                                                                                                                   | 0°C        |

| Junction Temperature55°C to +150                                                                                                                                                                                                                                        | )°C        |

| Lead Temperature (Soldering, 10 sec.) +300                                                                                                                                                                                                                              | )°C        |

| Note: Pin references are to 20 pin packages. All voltages a<br>with respect to ground. Currents are positive into, ne<br>ative out of, device terminals. Consult Unitrode<br>databook for information regarding thermal specifica<br>tions and limitations of packages. | are<br>9g- |

|                                                                                                                                                                                                                                                                         |            |

| Device | UVLO<br>Turn-On | UVLO<br>Turn-Off | Delay<br>Set |

|--------|-----------------|------------------|--------------|

| UC1875 | 10.75           | 9.25V            | Yes          |

| UC1876 | 15.25V          | 9.25V            | Yes          |

| UC1877 | 10.75V          | 9.25V            | No           |

| UC1878 | 15.25V          | 9.25V            | No           |

#### CONNECTION DIAGRAMS

N/C

## UC1875/6/7/8 UC2875/6/7/8 UC3875/6/7/8

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated,  $-55^{\circ}C < T_A < 125^{\circ}C$  for the UC1875/6/7/8,  $-25^{\circ}C < T_A < 85^{\circ}C$  for the UC2875/6/7/8 and  $0^{\circ}C < T_A < 70^{\circ}C$  for the UC3875/6/7/8, VC = VIN = 12V, R<sub>FREQSET</sub> =  $12k\Omega$ , C<sub>FREQSET</sub> = 330pF, R<sub>SI OPF</sub> =  $12k\Omega$ , C<sub>RAMP</sub> = 200pF, C<sub>DELAYSET A-B</sub> = C<sub>DELAYSET C-D</sub> =  $0.01\mu$ F, I<sub>DELAYSET A-B</sub> = I<sub>DELAYSET C-D</sub> =  $-500\mu$ A, T<sub>A</sub> = T<sub>J</sub>.

| PARAMETER               | TEST CONDITIONS                                                     | MIN  | TYP   | MAX   | UNITS |

|-------------------------|---------------------------------------------------------------------|------|-------|-------|-------|

| Undervoltage Lockout    |                                                                     |      |       | _     |       |

| Start Threshold         | UC1875/UC1877                                                       |      | 10.75 | 11.75 | V     |

|                         | UC1876/UC1878                                                       | -    | 15.25 | 1000  | V     |

| UVLO Hysteresis         | UC1875/UC1877                                                       | 0.5  | 1.25  | 2.0   | V     |

|                         | UC1876/UC1878                                                       |      | 6.0   |       | V     |

| Supply Current          |                                                                     |      |       |       |       |

| I <sub>IN</sub> Startup | VIN = 8V, VC = 20V, R <sub>SLOPE</sub> open, I <sub>DELAY</sub> = 0 |      | 150   | 600   | μΑ    |

| Ic Startup              | VIN = 8V, VC = 20V, R <sub>SLOPE</sub> open, I <sub>DELAY</sub> = 0 |      | 10    | 100   | μΑ    |

| lin                     |                                                                     |      | 30    | 44    | mA    |

| lc                      |                                                                     |      | 15    | 30    | mA    |

| Voltage Reference       |                                                                     |      |       |       |       |

| Output Voltage          | $T_J = +25^{\circ}C$                                                | 4.92 | 5     | 5.08  | V     |

| Line Regulation         | 11 < VIN < 20V                                                      |      | 1     | 10    | mV    |

| Load Regulation         | $I_{VREF} = -10 mA$                                                 |      | 5     | 20    | mV    |

| Total Variation         | Line, Load, Temperature                                             | 4.9  |       | 5.1   | V     |

| Noise Voltage           | 10Hz to 10kHz                                                       | -    | 50    |       | μVrms |

| Long Term Stability     | T <sub>J</sub> = 125°C, 1000 hours                                  |      | 2.5   |       | mV    |

| Short Circuit Current   |                                                                     | 60   | -     | mA    |       |

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated,  $-55^{\circ}C < T_A < 125^{\circ}C$  for the UC1875/6/7/8,  $-25^{\circ}C < T_A < 85^{\circ}C$  for the UC2875/6/7/8 and  $0^{\circ}C < T_A < 70^{\circ}C$  for the UC3875/6/7/8, VC = VIN = 12V, R<sub>FREQSET</sub> = 12k $\Omega$ , C<sub>FREQSET</sub> = 330pF, R<sub>SLOPE</sub> = 12k $\Omega$ , C<sub>RAMP</sub> = 200pF, C<sub>DELAYSET A-B</sub> = C<sub>DELAYSET C-D</sub> = 0.01 $\mu$ F, I<sub>DELAYSET A-B</sub> = I<sub>DELAYSET C-D</sub> = -500 $\mu$ A, T<sub>A</sub> = T<sub>J</sub>.

| PARAMETER                            | TEST CONDITIONS                                       | MIN  | TYP   | MAX  | UNITS  |

|--------------------------------------|-------------------------------------------------------|------|-------|------|--------|

| Error Amplifier                      |                                                       |      | _     |      |        |

| Offset Voltage                       |                                                       |      | 5     | 15   | mV     |

| Input Bias Current                   |                                                       |      | 0.6   | 3    | μΑ     |

| AVOL                                 | $1V < V_{E/AOUT} < 4V$                                | 60   | 90    |      | dB     |

| CMRR                                 | 1.5V < V <sub>CM</sub> < 5.5V                         | 75   | 95    |      | dB     |

| PSRR                                 | 11V < VIN < 20V                                       | 85   | 100   | 1.1  | dB     |

| Output Sink Current                  | $V_{E/AOUT} = 1V$                                     | 1    | 2.5   |      | mA     |

| Output Source Current                | $V_{E/AOUT} = 4V$                                     |      | -1.3  | -0.5 | mA     |

| Output Voltage High                  | $I_{E/AOUT} = -0.5 mA$                                | 4    | 4.7   | 5    | V      |

| Output Voltage Low                   | $I_{E/AOUT} = 1 m A$                                  | 0    | 0.5   | 1    | V      |

| Unity Gain BW                        | (Note 8)                                              | 7    | 11    |      | MHz    |

| Slew Rate                            | (Note 8)                                              | 6    | 11    |      | V/µsec |

| PWM Comparator                       |                                                       |      |       |      |        |

| Ramp Offset Voltage                  | T <sub>J</sub> = 25°C (Note 3)                        |      | 1.3   |      | V      |

| Zero Phase Shift Voltage             | (Note 4)                                              | 0.55 | 0.9   | 1    | V      |

| PWM Phase Shift (Note1) and (Note 7) | V <sub>E/AOUT</sub> > (Ramp Peak + Ramp Offset)       | 98   | 99.5  | 102  | %      |

|                                      | V <sub>E/AOUT</sub> < Zero Phase Shift Voltage        | 0    | 0.5   | 2    | %      |

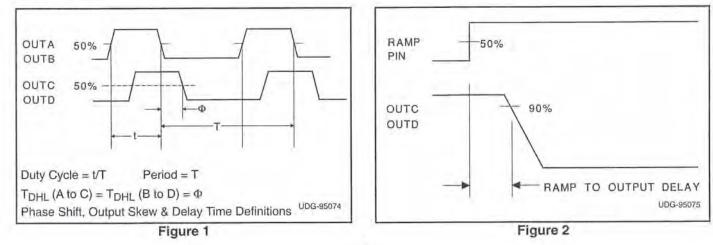

| Output Skew (Note 1) and (Note 7)    | V <sub>E/AOUT</sub> < 1V                              |      | 5     | ±20  | nsec   |

| Ramp to Output Delay, (Note 8)       | UC3875/6/7/8 (Note 6)                                 |      | 65    | 100  | nsec   |

|                                      | UC1875/6/7/8, UC2875/6/7/8 (Note 6)                   |      | 65    | 125  | nsec   |

| Oscillator                           |                                                       |      |       |      |        |

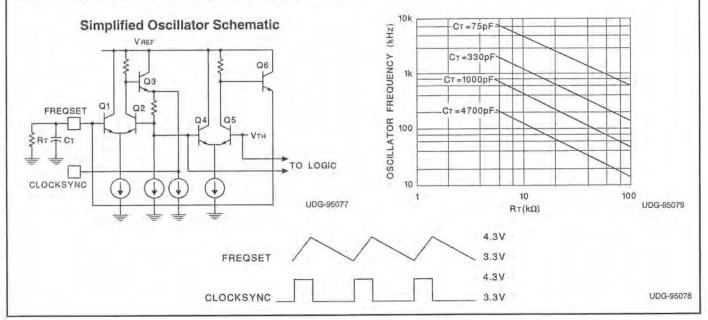

| Initial Accuracy                     | $T_J = 25^{\circ}C$                                   | 0.85 | 1     | 1.15 | MHz    |

| Voltage Stability                    | 11V < VIN < 20V                                       |      | 0.2   | 2    | %      |

| Total Variation                      | Line, Temperature                                     | 0.80 | 1     | 1.20 | MHz    |

| Sync Pin Threshold                   | $T_J = 25^{\circ}C$                                   |      | 3.8   |      | V      |

| Clock Out Peak                       | $T_J = 25^{\circ}C$                                   |      | 4.3   |      | V      |

| Clock Out Low                        | $T_J = 25^{\circ}C$                                   |      | 3.3   |      | V      |

| Clock Out Pulse Width                | $R_{CLOCKSYNC} = 3.9 k\Omega$                         |      | 30    | 100  | nsec   |

| Maximum Frequency, (Note 7)          | $R_{FREQSET} = 5k\Omega$                              | 2    | 1     |      | MHz    |

| Ramp Generator/Slope Compensation    |                                                       |      |       |      |        |

| Ramp Current, Minimum                | $I_{SLOPE} = 10\mu A$ , $V_{FREQSET} = VREF$          |      | -11   | -14  | μΑ     |

| Ramp Current, Maximum                | I <sub>SLOPE</sub> = 1mA, V <sub>FREQSET</sub> = VREF | -0.8 | -0.95 |      | mA     |

| Ramp Valley                          |                                                       |      | 0     |      | V      |

| Ramp Peak - Clamping Level           | $R_{FREQSET} = 100 k\Omega$                           | 3.8  | 4.1   | 5.0  | V      |

| Current Limit                        |                                                       |      |       |      | -      |

| Input Bias                           | $V_{CS}$ + = 3V                                       |      | 2     | 5    | μΑ     |

| Threshold Voltage                    |                                                       | 2.4  | 2.5   | 2.6  | V      |

| Delay to Output, (Note 8)            | UC3875/6/7/8                                          |      | 85    | 125  | nsec   |

|                                      | UC1875/6/7/8, UC2875/6/7/8                            |      | 85    | 150  | nsec   |

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated,  $-55^{\circ}C < T_A < 125^{\circ}C$  for the UC1875/6/7/8,  $-25^{\circ}C < T_A < 85^{\circ}C$  for the UC2875/6/7/8 and  $0^{\circ}C < T_A < 70^{\circ}C$  for the UC3875/6/7/8, VC = VIN = 12V, R<sub>FREQSET</sub> =  $12k\Omega$ , C<sub>FREQSET</sub> = 330pF, R<sub>SLOPE</sub> =  $12k\Omega$ , C<sub>RAMP</sub> = 200pF, C<sub>DELAYSET A-B</sub> = C<sub>DELAYSET C-D</sub> =  $0.01\mu$ F, I<sub>DELAYSET A-B</sub> = I<sub>DELAYSET C-D</sub> =  $-500\mu$ A, T<sub>A</sub> = T<sub>J</sub>.

| PARAMETER                        | TEST CONDITIONS                                                      | MIN | TYP | MAX | UNITS |

|----------------------------------|----------------------------------------------------------------------|-----|-----|-----|-------|

| Soft-Start/Reset Delay           |                                                                      |     |     |     |       |

| Charge Current                   | V <sub>SOFTSTART</sub> = 0.5V                                        | -20 | -9  | -3  | μA    |

| Discharge Current                | VSOFTSTART = 1V                                                      | 120 | 230 |     | μΑ    |

| Restart Threshold                |                                                                      | 4.3 | 4.7 |     | V     |

| Discharge Level                  |                                                                      | _   | 300 | 1   | mV    |

| Output Drivers                   |                                                                      |     |     |     |       |

| Output Low Level                 | I <sub>OUT</sub> = 50mA                                              | -   | 0.2 | 0.4 | V     |

|                                  | $I_{OUT} = 500 \text{mA}$                                            |     | 1.2 | 2.6 | V     |

| Output High Level                | $I_{OUT} = -50 \text{mA}$                                            |     | 1.5 | 2.5 | V     |

|                                  | $I_{OUT} = -500 \text{mA}$                                           | 1   | 1.7 | 2.6 | V     |

| Delay Set (UC1875 and UC1876 onl | y)                                                                   |     |     | _   |       |

| Delay Set Voltage                | $I_{DELAY} = -500 \mu A$                                             | 2.3 | 2.4 | 2.6 | V     |

| Delay Time, (Note 8)             | I <sub>DELAY</sub> = -250μA (Note 5) (UC3875/6/7/8,<br>UC2875/6/7/8) | 150 | 250 | 400 | nsec  |

|                                  | I <sub>DELAY</sub> = -250µA (Note 5) (UC1875/6/7/8)                  | 150 | 250 | 600 | nsec  |

Note 1: Phase shift percentage (0% = 0°, 100% = 180°) is defined as  $\theta = \frac{200}{T} \Phi$ %, where  $\theta$  is the phase shift, and  $\Phi$  and T are defined in Figure 1. At 0% phase shift,  $\Phi$  is the output skew.

Note 2: Delay time is defined as delay = T (1/2-(duty cycle)), where T is defined in Fig. 1.

Note 3: Ramp offset voltage has a temperature coefficient of about -4mV/°C.

Note 4: Zero phase shift voltage has a temperature coefficient of about -2mV/°C.

Note 5: Delay time can be programmed via resistors from the delay set pins to ground. Delay time  $\approx \frac{62.5 \cdot 10^{-12}}{r}$  sec. Where

DELAY

$I_{DELAY} = \frac{Delay \ set \ voltage}{R_{DELAY}}$  The recommended range for  $I_{DELAY}$  is  $25\mu A \le I_{DELAY} \le 1mA$

Note 6: Ramp delay to output time is defined in Fig. 2.

Note 7: Not production tested at -55°C.

Note 8: Not production tested.

#### PIN DESCRIPTIONS

**CLOCKSYNC (bi-directional clock and synchronization pin):** Used as an output, this pin provides a clock signal. As an input, this pin provides a synchronization point. In its simplest usage, multiple devices, each with their own local oscillator frequency, may be connected together by the CLOCKSYNC pin and will synchronize on the fastest oscillator. This pin may also be used to synchronize the device to an external clock, provided the external signal is of higher frequency than the local oscillator. A resistor load may be needed on this pin to minimize the clock pulse width.

**E/AOUT (error amplifier output):** This is is the gain stage for overall feedback control. Error amplifier output voltage levels below 1 volt will force 0° phase shift. Since the error amplifier has a relatively low current drive capability, the output may be overridden by driving with a sufficiently low impedance source.

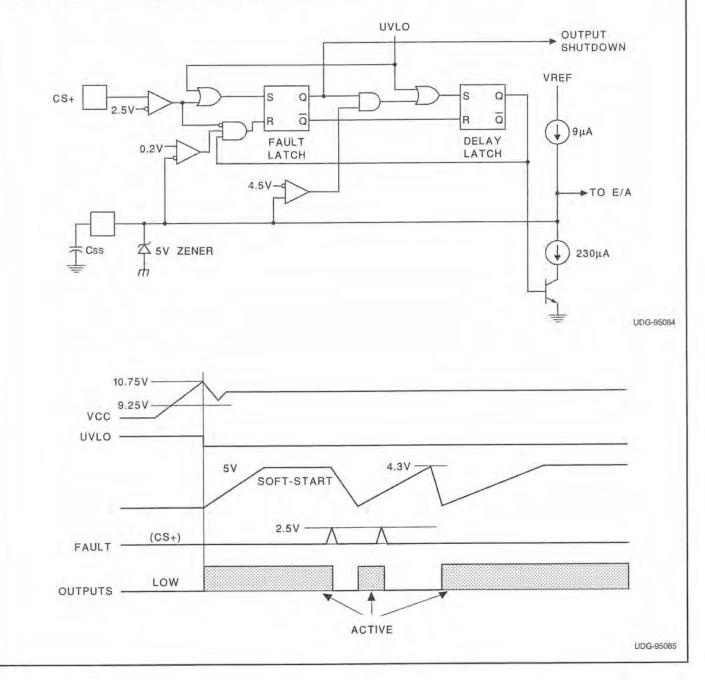

**CS+ (current sense):** The non-inverting input to the current-fault comparator whose reference is set internally to a fixed 2.5V (separate from VREF). When the voltage at this pin exceeds 2.5V the current-fault latch is set, the outputs are forced OFF and a SOFT-START cycle is initiated. If a constant voltage above 2.5V is applied to this pin the outputs are disabled from switching and held in a low state until the CS+ pin is brought below 2.5V. The outputs may begin switching at 0 degrees phase shift before the SOFTSTART pin begins to rise -- this condition will not prematurely deliver power to the load.

FREQSET (oscillator frequency set pin): A resistor and a capacitor from FREQSET to GND will set the oscillator frequency.

DELAYSET A-B, DELAYSET C-D (output delay control): The user programmed current flowing from these pins to GND set the turn-on delay for the corresponding output pair. This delay is introduced between turn-off of one switch and turn-on of another in the same leg of the bridge to provide a dead time in which the resonant switching of the external power switches takes place. Separate delays are provided for the two half-bridges to accommodate differences in the resonant capacitor charging currents.

EA- (error amplifier inverting input): This is normally connected to the voltage divider resistors which sense the power supply output voltage level.

EA+ (error amplifier non-inverting input): This is normally connected to a reference voltage used for comparison with the sensed power supply output voltage level at the EA+ pin.

GND (signal ground): All voltages are measured with respect to GND. The timing capacitor, on the FREQSET

pin, any bypass capacitor on the VREF pin, bypass capacitors on VIN and the ramp capacitor, on the RAMP pin, should be connected directly to the ground plane near the signal ground pin.

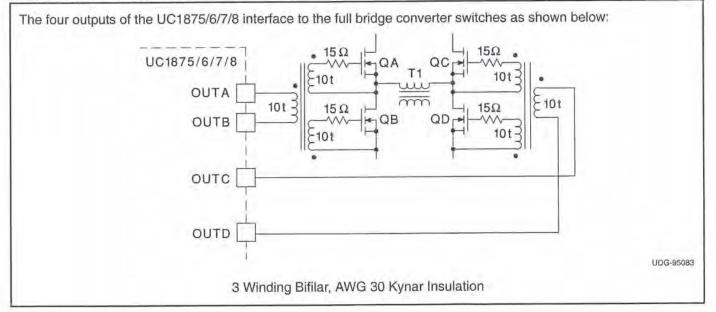

**OUTA-OUTD** (outputs A-D): The outputs are 2A totem-pole drivers optimized for both MOSFET gates and level-shifting transformers. The outputs operate as pairs with a nominal 50% duty-cycle. The A-B pair is intended to drive one half-bridge in the external power stage and is syncronized with the clock waveform. The C-D pair will drive the other half-bridge with switching phase shifted with respect to the A-B outputs.

**PWRGND (power ground):** VC should be bypassed with a ceramic capacitor from the VC pin to the section of the ground plane that is connected to PWRGND. Any required bulk reservoir capacitor should parallel this one. Power ground and signal ground may be joined at a single point to optimize noise rejection and minimize DC drops.

**RAMP (voltage ramp):** This pin is the input to the PWM comparator. Connect a capacitor from here to GND. A voltage ramp is developed at this pin with a slope:

| dV | Sense Voltage                          |  |

|----|----------------------------------------|--|

| dT | R <sub>SLOPE</sub> • C <sub>RAMP</sub> |  |

Current mode control may be achieved with a minimum amount of external circuitry, in which case this pin provides slope compensation.

Because of the 1.3V offset between the ramp input and the PWM comparator, the error amplifier output voltage can not exceed the effective ramp peak voltage and duty cycle clamping is easily achievable with appropriate values of R<sub>SLOPE</sub> and C<sub>RAMP</sub>.

SLOPE (set ramp slope/slope compensation): A resistor from this pin to VCC will set the current used to generate the ramp. Connecting this resistor to the DC input line voltage will provide voltage feed-forward.

**SOFTSTART (soft start):** SOFTSTART will remain at GND as long as VIN is below the UVLO threshold. SOFTSTART will be pulled up to about 4.8V by an internal  $9\mu$ A current source when VIN becomes valid (assuming a non-fault condition). In the event of a current-fault (CS+ voltage exceeding 2.5V), SOFTSTART will be pulled to GND and them ramp to 4.8V. If a fault occurs during the SOFTSTART cycle, the outputs will be immediately disabled and SOFTSTART must charge fully prior to resetting the fault latch.

For paralleled controllers, the SOFTSTART pins may be paralled to a single capacitor, but the charge currents will be additive.

## UC1875/6/7/8 UC2875/6/7/8 UC3875/6/7/8

#### PIN DESCRIPTIONS (cont.)

VC (output switch supply voltage): This pin supplies power to the output drivers and their associated bias circuitry. Connect VC to a stable source above 3V for normal operation, above 12V for best performance. This supply should be bypassed directly to the PWRGND pin with low ESR, low ESL capacitors.

VIN (primary chip supply voltage): This pin supplies power to the logic and analog circuitry on the integrated circuit that is not directly associated with driving the output stages. Connect VIN to a stable source above 12V for normal operation. To ensure proper chip functionality, these devices will be inactive until VIN exceeds the upper undervoltage lockout threshold. This pin should by bypassed directly to the GND pin with low ESR, low ESL capacitors. NOTE: When VIN exceeds the UVLO threshold the supply current ( $I_{IN}$ ) will jump from about 100µA to a current in excess of 20µA. If the UC1875 is not connected to a well bypassed supply, it may immediately enter UVLO again.

**VREF:** This pin is an accurate 5V voltage reference. This output is capable of delivering about 60mA to peripheral circuitry and is internally short circuit current limited. VREF is disabled while VIN is low enough to force the chip into UVLO. The circuit is also in UVLO until VREF reaches approximately 4.75V. For best results bypass VREF with a  $0.1\mu$ F, low ESR, low ESL, capacitor to the GND pin.

#### APPLICATION INFORMATION Undervoltage Lockout Section

When power is applied to the circuit and VIN is below the upper UVLO threshold,  $I_{IN}$  will be below 600µA, the reference generator will be off, the fault latch is reset, the soft-start pin is discharged, and the outputs are actively held low. When VIN exceeds the upper UVLO threshold, the reference generator turns on. All else remains in the shut-down mode until the output of the reference, VREF, exceeds 4.75V.

UDG-99136

The high frequency oscillator may be either free-running or externally synchronized. For free-running operation, the frequency is set via an ex-

ternal resistor and capacitor to ground from the FREQSET pin.

## APPLICATION INFORMATION (cont.) Synchronizing The Oscillator

cuitry, as shown in the previous figure.

## UC1875/6/7/8 UC2875/6/7/8 UC3875/6/7/8

### APPLICATION INFORMATION (cont.) Delay Blocks And Output Stages

In each of the output stages, transistors Q3 through Q6 form a high-speed totem-pole driver which will source or sink more than one amp peak with a total delay of approximately 30 nanoseconds. To ensure a low output level prior to turn-on, transistors Q7 through Q9 form a self-biased driver to hold Q6 on prior to the supply reaching its turn-on threshold. This circuit is operable when the chip supply is zero. Q6 is also turned on and held low with a signal from the fault logic portion of the chip.

C1 which must discharge to VTH before the output can go high. The time is defined by the current sources, I1, which is programmed by an external resistor, R<sub>TD</sub>. The voltage on the Delay Set pins is internally regulated to to disable the delay circuitry, and the delay time must be programmed.

#### Output Switch Orientation

#### APPLICATION INFORMATION (cont.) Fault/Soft-Start

The fault control circuitry provides two forms of power shutdown:

- · Complete turn-off of all four output power stages.

- · Clamping the phase shift command to zero.

Complete turn-off is ordered for an over-current fault or a low supply voltage. When the SOFTSTART pin reaches its low threshold, switching is allowed to proceed while the phase-shift is advanced from zero to its nominal value with the time constant of the SOFT-START capacitor.

The fault logic insures that a continuous fault will institute a low frequency "hiccup" retry cycle by forcing the SOFT-START capacitor to charge through its full cycle between each restart attempt.

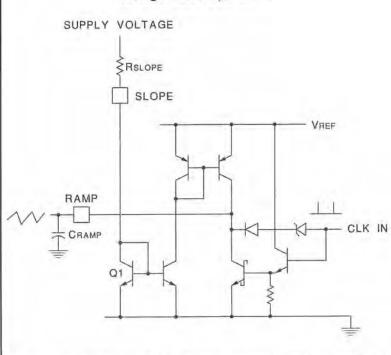

#### APPLICATIONS INFORMATION (cont.) Slope/Ramp Pins

The ramp generator may be configured for the following control methods: The figure below shows a voltage-mode configuration. With R<sub>SLOPE</sub> tied to a stable voltage source, the wave-

- Voltage Mode

- Voltage Feedforward

- Current Mode

- Current Mode with Slope Compensation

Voltage Mode Operation

With  $R_{SLOPE}$  tied to a stable voltage source, the waveform on  $C_{RAMP}$  will be a constant-slope ramp, providing conventional voltage-mode control. If  $R_{SLOPE}$  is connected to the power supply input voltage, a variable-slope ramp will provide voltage feedforward.

1. Simple voltage mode operation achieved by placing  ${\sf R}_{\sf SLOPE}$  between VIN and SLOPE.

2. Voltage Feedforward achieved by placing  $R_{SLOPE}$  between supply voltage and SLOPE pin of UC1875.

RAMP

$$\frac{dV}{dT} \approx \frac{V_{Rslope}}{R_{SLOPE} \bullet C_{RAMP}}$$

UDG-95086

For current-mode control the ramp generator may be disabled by grounding the slope pin and using the ramp pin as a direct current sense input to the PWM comparator.

17-Dec-2007

#### **PACKAGING INFORMATION**

TEXAS INSTRUMENTS www.ti.com

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| 5962-9455501M3A  | ACTIVE                | LCCC            | FK                 | 28   | 1              | TBD                       | POST-PLATE       | N / A for Pkg Type           |

| 5962-9455501MRA  | ACTIVE                | CDIP            | J                  | 20   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| 5962-9455501MXA  | OBSOLETE              | TO-92           | LP                 | 28   |                | TBD                       | Call TI          | N / A for Pkg Type           |

| 5962-9455501V3A  | ACTIVE                | LCCC            | FK                 | 28   | 1              | TBD                       | POST-PLATE       | N / A for Pkg Type           |

| 5962-9455501VRA  | ACTIVE                | CDIP            | J                  | 20   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| UC1875J          | ACTIVE                | CDIP            | J                  | 20   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| UC1875J883B      | ACTIVE                | CDIP            | J                  | 20   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| UC1875JQMLV      | ACTIVE                | CDIP            | J                  | 20   |                | TBD                       | Call TI          | Call TI                      |

| UC1875L          | ACTIVE                | LCCC            | FK                 | 28   | 1              | TBD                       | POST-PLATE       | N / A for Pkg Type           |

| UC1875L883B      | ACTIVE                | LCCC            | FK                 | 28   | 1              | TBD                       | POST-PLATE       | N / A for Pkg Type           |

| UC2875DWP        | ACTIVE                | SOIC            | DW                 | 28   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2875DWPG4      | ACTIVE                | SOIC            | DW                 | 28   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2875DWPTR      | ACTIVE                | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2875DWPTRG4    | ACTIVE                | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2875J          | ACTIVE                | CDIP            | J                  | 20   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| UC2875N          | ACTIVE                | PDIP            | Ν                  | 20   | 20             | Green (RoHS & no Sb/Br)   | Call TI          | N / A for Pkg Type           |

| UC2875NG4        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | Green (RoHS & no Sb/Br)   | Call TI          | N / A for Pkg Type           |

| UC2875QP         | ACTIVE                | PLCC            | FN                 | 28   | 37             | TBD                       | Call TI          | Level-2-220C-1 YEAR          |

| UC2876N          | ACTIVE                | PDIP            | Ν                  | 20   | 20             | Green (RoHS & no Sb/Br)   | Call TI          | N / A for Pkg Type           |

| UC2876NG4        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | Green (RoHS & no Sb/Br)   | Call TI          | N / A for Pkg Type           |

| UC3875DWP        | ACTIVE                | SOIC            | DW                 | 28   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3875DWPG4      | ACTIVE                | SOIC            | DW                 | 28   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3875DWPTR      | ACTIVE                | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3875DWPTRG4    | ACTIVE                | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3875N          | ACTIVE                | PDIP            | Ν                  | 20   | 20             | Green (RoHS & no Sb/Br)   | Call TI          | N / A for Pkg Type           |

| UC3875NG4        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | Green (RoHS & no Sb/Br)   | Call TI          | N / A for Pkg Type           |

| UC3875QP         | ACTIVE                | PLCC            | FN                 | 28   | 37             | TBD                       | Call TI          | Level-2-220C-1 YEAR          |

| UC3876N          | ACTIVE                | PDIP            | Ν                  | 20   | 20             | Green (RoHS & no Sb/Br)   | Call TI          | N / A for Pkg Type           |

| UC3876NG4        | ACTIVE                | PDIP            | Ν                  | 20   | 20             | Green (RoHS & no Sb/Br)   | Call TI          | N / A for Pkg Type           |

| UC3877DWPTR      | ACTIVE                | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Pa | ackage<br>Qty | Eco Plan <sup>(2)</sup>    | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------|---------------|----------------------------|------------------|------------------------------|

| UC3877DWPTRG4    | ACTIVE                | SOIC            | DW                 | 28      | 1000          | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. **TBD**: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

TEXAS INSTRUMENTS www.ti.com

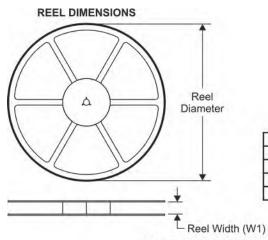

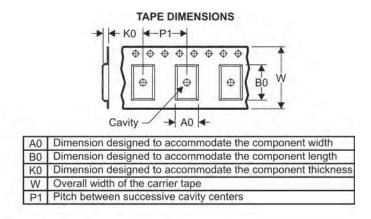

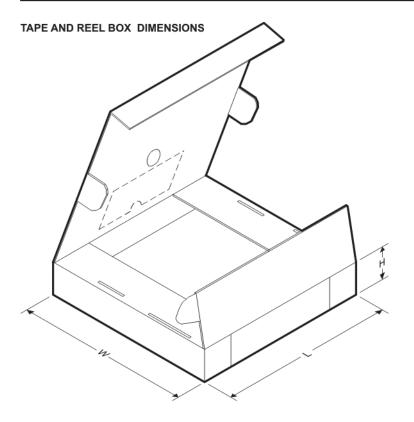

### TAPE AND REEL INFORMATION

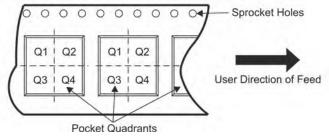

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are | nominal        |                      |    |      |                          |                          |         |         |         |            |           |                  |

|---------------------|----------------|----------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| Device              | Packag<br>Type | e Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| UC2875DWP           | TR SOIC        | DW                   | 28 | 1000 | 330.0                    | 32.4                     | 11.35   | 18.67   | 3.1     | 16.0       | 32.0      | Q1               |

| UC3875DWP           | TR SOIC        | DW                   | 28 | 1000 | 330.0                    | 32.4                     | 11.35   | 18.67   | 3.1     | 16.0       | 32.0      | Q1               |

| UC3877DWP           | TR SOIC        | DW                   | 28 | 1000 | 330.0                    | 32.4                     | 11.35   | 18.67   | 3.1     | 16.0       | 32.0      | Q1               |

## PACKAGE MATERIALS INFORMATION

11-Mar-2008

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC2875DWPTR | SOIC         | DW              | 28   | 1000 | 346.0       | 346.0      | 49.0        |

| UC3875DWPTR | SOIC         | DW              | 28   | 1000 | 346.0       | 346.0      | 49.0        |

| UC3877DWPTR | SOIC         | DW              | 28   | 1000 | 346.0       | 346.0      | 49.0        |

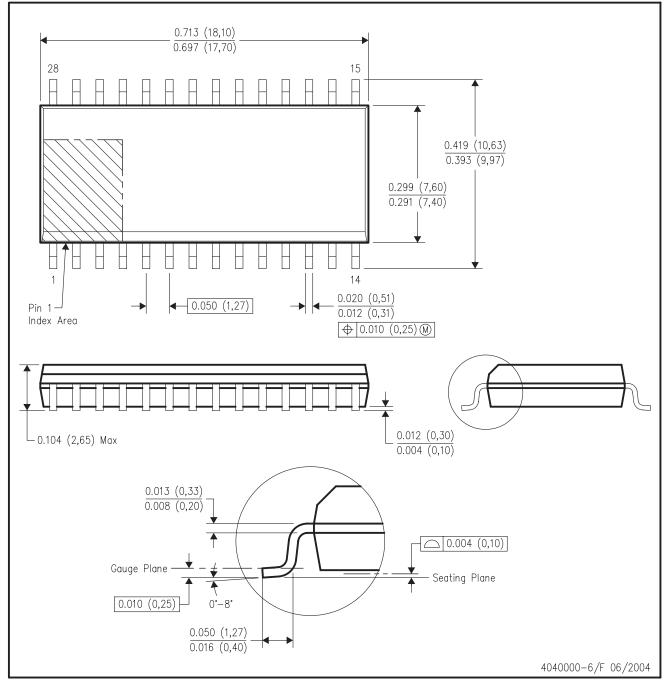

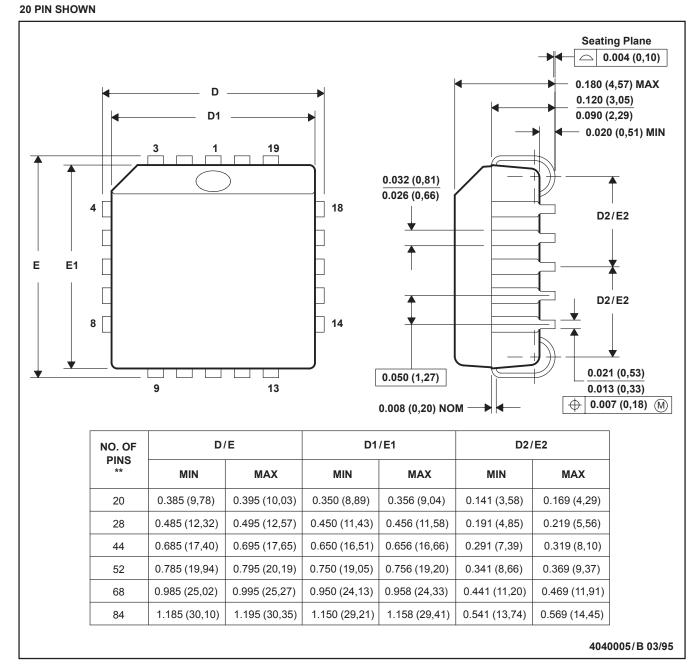

DW (R-PDSO-G28)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013 variation AE.

MLCC006B - OCTOBER 1996

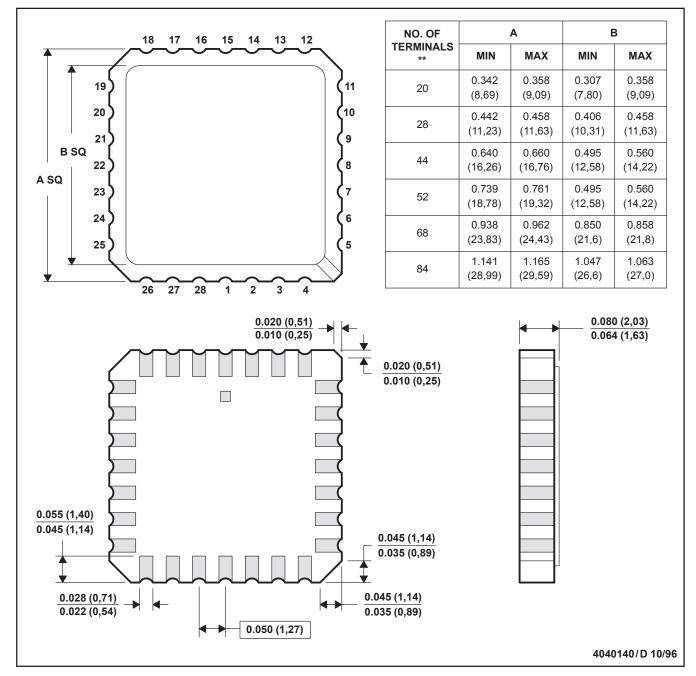

#### FK (S-CQCC-N\*\*)

#### LEADLESS CERAMIC CHIP CARRIER

**28 TERMINAL SHOWN**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a metal lid.

- D. The terminals are gold plated.

- E. Falls within JEDEC MS-004

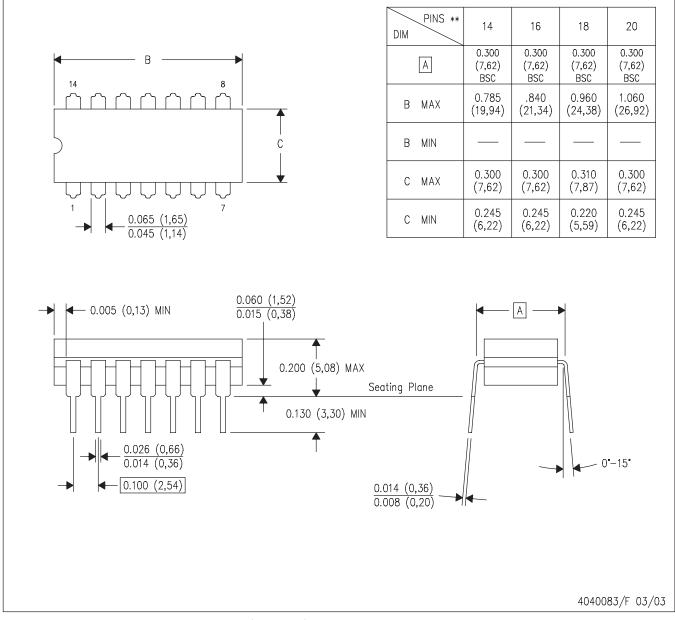

J (R-GDIP-T\*\*) 14 LEADS SHOWN

CERAMIC DUAL IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package is hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

- E. Falls within MIL STD 1835 GDIP1-T14, GDIP1-T16, GDIP1-T18 and GDIP1-T20.

## **MECHANICAL DATA**

MPLC004A - OCTOBER 1994

#### PLASTIC J-LEADED CHIP CARRIER

## FN (S-PQCC-J\*\*)

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-018

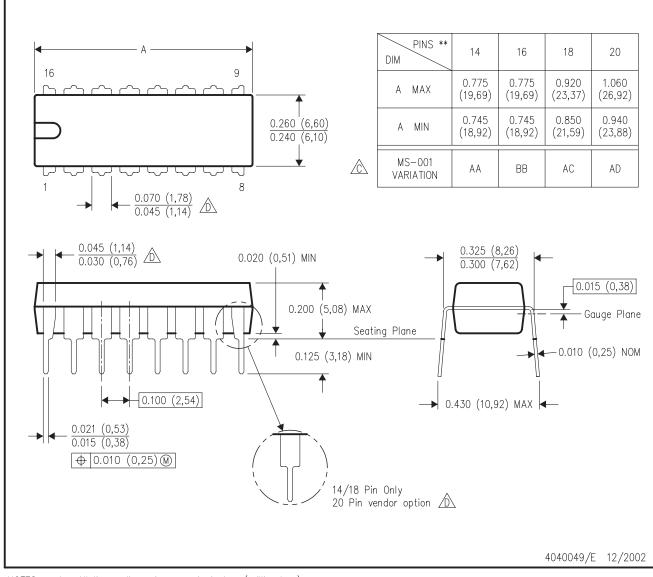

## N (R-PDIP-T\*\*)

PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- $\triangle$  The 20 pin end lead shoulder width is a vendor option, either half or full width.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                         | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Clocks and Timers           | www.ti.com/clocks      | Digital Control    | www.ti.com/digitalcontrol |

| Interface                   | interface.ti.com       | Medical            | www.ti.com/medical        |

| Logic                       | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt                  | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers            | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                        | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video & Imaging    | www.ti.com/video          |

|                             |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated